Visible to Intel only — GUID: llv1497992668942

Ixiasoft

Add Clock, Reset, and Avalon-MM components

Add Pre-Built Systems and Memory Test Microcore Components

Export Signals, Set Base Address Assignments, and Connect Memory Tester Interface Components

Resolve Interface Requirements and Value Mismatches

Replace the memory_tester_subsystem Generic Component

Synchronize IP Results

Visible to Intel only — GUID: llv1497992668942

Ixiasoft

Add RAM, JTAG UART, and Avalon-MM Pipeline Bridge

The final components you'll need to add and configure are an On-Chip RAM, a JTAG UART, and an Avalon-MM Pipeline Bridge.

- Type ram in the IP Catalog search box and double-click On-Chip Memory (RAM or ROM).

- In the On-Chip Memory (RAM or ROM) parameter editor, in the Size box, set the Total memory size to 8192 bytes.

- To add the On-Chip Memory (RAM or ROM) component to your design, click Finish.

- Right-click the name of the On-Chip Memory (RAM or ROM) component and click Rename. Type onchip_ram to change the name.

- Type jtag uart in the IP Catalog search box and double-click JTAG UART.

- To add the JTAG UART component to your design with default settings, click Finish.

- Right-click the name of the JTAG UART component and click Rename. Type jtag_uart to change the name.

- Type pipeline bridge in the IP Catalog search box and double-click Avalon-MM Pipeline Bridge.

- In the Avalon-MM Pipeline Bridge parameter editor, change the following settings:

- Set the Address width to 16.

- Set the Maximum pending read transactions to 1.

- To add the Avalon-MM Pipeline Bridge to your design, click Finish.

- Right-click the name of the Avalon-MM Pipeline Bridge component and click Rename. Type pipeline_bridge to change the name.

- In the Export column, double-click the entry that corresponds to the m0 signal for the pipeline_bridge component and type master.

The Avalon-MM Pipeline Bridge allows the processor subsystem cpu_subsystem to export a single Avalon-MM master interface. Your design can then access the slave interfaces in a higher-level system, and handle address offsets automatically. The bridge also improves timing performance.

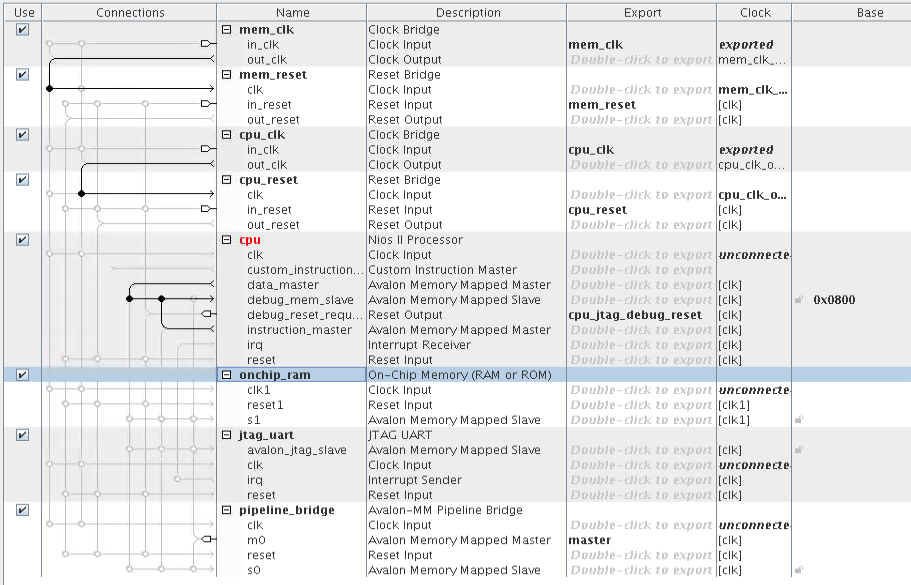

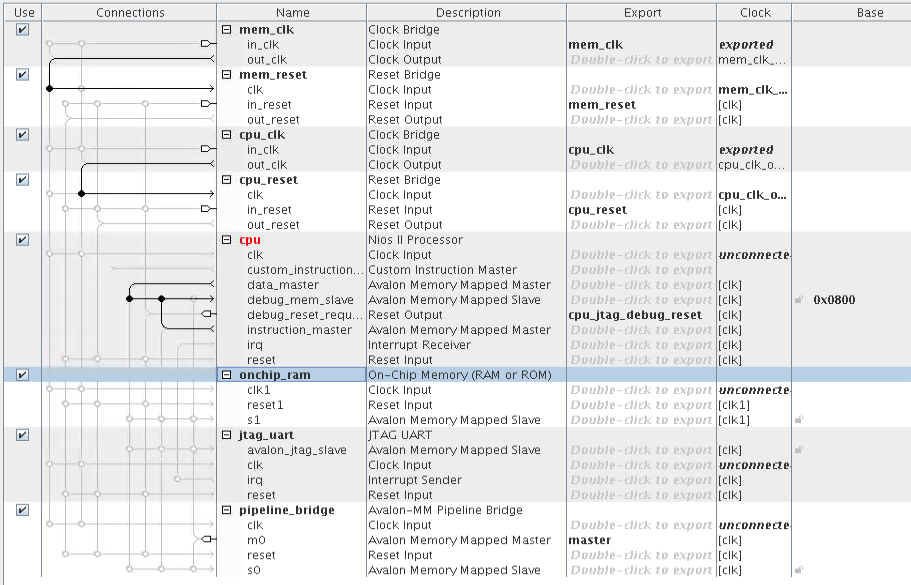

All the required components are now included in this subsystem. Compare the settings in your design with the following figure and make sure your components and exported interfaces are named correctly.

Figure 10. Export Names for cpu_subsystem Components