Visible to Intel only — GUID: mij1548189456191

Ixiasoft

Visible to Intel only — GUID: mij1548189456191

Ixiasoft

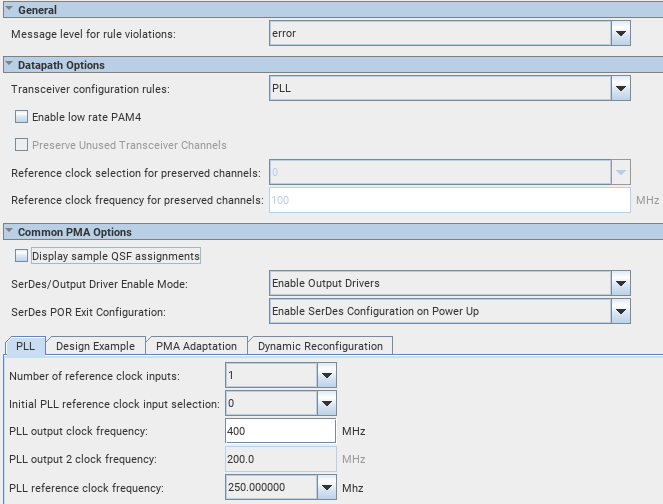

2.2.11. PLL Mode

PLL mode is a configuration of the E-tile transceiver Native PHY IP core that configures the E-tile transceiver as a PLL. It is used for external EMIB clocking configurations (see the use case in Four 25 Gbps PMA Direct Channel (with FEC) within a Single FEC Block ). It does not support dynamic reconfiguring between PLL and other Transceiver Configuration Rules.

After a transceiver channel is used in PLL mode, it cannot be used for a usual transceiver operation. You have to connect the output of the Native PHY IP core in PLL mode to the respective transceiver input.

| Parameter | Value | Description |

|---|---|---|

| Number of reference clock inputs | 1, 2, 3, 4, 5 | Specifies the desired number of reference clocks. The Native PHY IP core presents up to five clock inputs. |

| Initial TX reference clock input selection | Based on the number of reference clock input | Specifies the initially selected PLL reference clock input. This indicates the starting clock input selection used for this configuration when dynamically switching between multiple TX reference clock inputs. |

| PLL output clock frequency | 100 - 1000 MHz | Specifies the PLL output frequency in units of MHz. |

| PLL output 2 clock frequency | Output from the PLL. pll_clkout2 frequency = 0.5 * pll_clkout1 frequency |

Specifies the PLL output frequency for output 2 in units of MHz. |

| PLL reference clock frequency | Refer to the Device Data Sheet. | Selects the reference clock frequency for the PLL. |

PLL output clock (pll_clkout) and PLL output 2 clock (pll_clkout2) are asynchronous (no phase relationship) to each other and to any other clock output from the Native PHY IP. You need to take the required precautions to do any data transfers between the two clocks.

| Port Name | Direction | Clock Domain | Width | Description |

|---|---|---|---|---|

| pll_refclk0 pll_refclk1 pll_refclk2 pll_refclk3 pll_refclk4 |

Input | N/A | 1 bit for each channel | Reference clock for the PLL. |

| pll_locked | Output | reconfig_clk | 1 bit for each channel | Locked status signal of the PLL. When you use the PLL channel as a clock source to the transceiver channel through external EMIB clocking:

|

| tx_serial_data | Output | N/A | 1 bit for each channel | The tx_serial_data port is only used to assign the location of the PLL channel. It is not an active port for transmitting data.10 |

| pll_clkout1 pll_clkout2 |

Output | N/A | 1 bit for each channel | Output from the PLL. pll_clkout2 frequency = 0.5 * pll_clkout1 frequency |

set_location_assignment HSSIXCVR_4T9A18 -to <path>|xcvr_native_s10_etile_0|g_xcvr_native_insts[0].ct3_xcvr_native_inst|inst_ct3_xcvr_channel|inst_ct3_hssi_xcvr