Visible to Intel only — GUID: iga1423336626008

Ixiasoft

Visible to Intel only — GUID: iga1423336626008

Ixiasoft

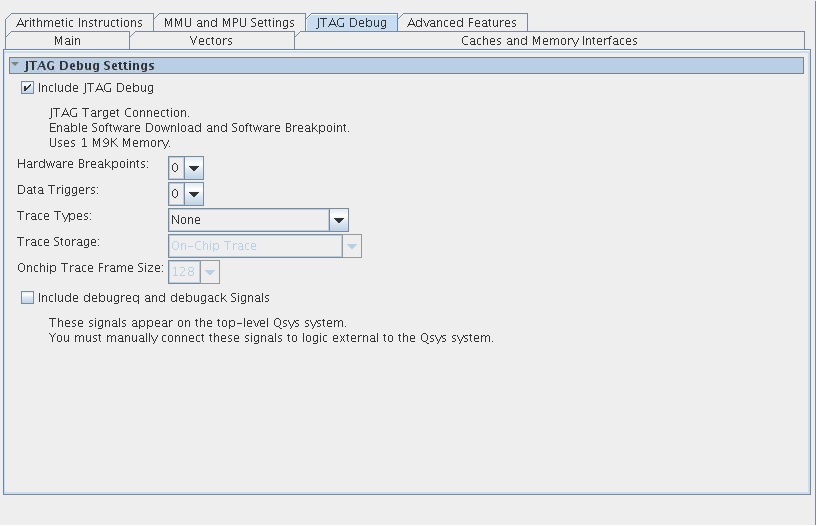

4.6. JTAG Debug Tab

The JTAG Debug tab presents settings for configuring the JTAG debug module on the Nios® II processor. You can select the debug features appropriate for your target application.

Soft processor cores such as the Nios® II processor offer unique debug capabilities beyond the features of traditional fixed processors. The soft nature of the Nios® II processor allows you to debug a system in development using a full-featured debug core, and later remove the debug features to conserve logic resources. For the release version of a product, you might choose to reduce the JTAG debug module functionality, or remove it altogether.

| Feature | Description |

|---|---|

| JTAG Target Connection | Connects to the processor through the standard JTAG pins on the Intel FPGA. This connection provides the basic capabilities to start and stop the processor, and examine/edit registers and memory. |

| Download Software | Downloads executable code to the processor’s memory via the JTAG connection. |

| Software Breakpoints | Sets a breakpoint on instructions residing in RAM. |

| Hardware Breakpoints | Sets a breakpoint on instructions residing in nonvolatile memory, such as flash memory. |

| Data Triggers | Triggers based on address value, data value, or read or write cycle. You can use a trigger to halt the processor on specific events or conditions, or to activate other events, such as starting execution trace, or sending a trigger signal to an external logic analyzer. Two data triggers can be combined to form a trigger that activates on a range of data or addresses. |

| Instruction Trace | Captures the sequence of instructions executing on the processor in real time. |

| Data Trace | Captures the addresses and data associated with read and write operations executed by the processor in real time. |

| On-Chip Trace | Stores trace data in on-chip memory. |

| Off-Chip Trace | Stores trace data in an external debug probe. Off-chip trace instantiates a PLL inside the Nios II core. Off-chip trace requires a debug probe from Imagination Technologies or Lauterbach GmbH. |

The Include debugreq and debugack signals debug signals setting provides the following functionality. When on, the Nios® II processor includes debug request and acknowledge signals. These signals let another device temporarily suspend the Nios® II processor for debug purposes. The signals are exported to the top level of your Platform Designer system.

For more information about the debug signals, refer to the Processor Architecture chapter of the Nios® II Processor Reference Handbook.

You can set the onchip trace buffer size to sizes from 128 to 64K trace frames, using OCI Onchip Trace. Larger buffer sizes consume more on-chip M4K RAM blocks. Every M4K RAM block can store up to 128 trace frames.