1.4.2. Test Case— Avalon® Streaming Reverse Loopback

To run the hardware test case, follow these steps:

- Download the reference design from Design Store and restore the design using Intel® Quartus® Prime software.

- Launch the Intel® Quartus® Prime software and open the project file (top.qpf).

- Click to compile the design.

- After the design is compiled successfully, a programming file (top.sof) is generated and located in the <project_directory>/output_files directory.

- Set up the Intel® Stratix® 10 GX L-Tile FPGA Development Board.

- Connect the external packet generator to the RJ-45 port of the development board (J10) by using Ethernet Cat5e cable.

- Connect the programming cable to the JTAG connection port (CN1).

- Connect the power adapter to the power supply input (J27).

- In the Intel® Quartus® Prime software, select to launch the programmer.

- Download the generated programming file (top.sof) to the development board using the Programmer application.

- Reset the Ethernet design by either these methods:

- Press the USER_PB0 push button.

- Toggle the In-System Source and Probes bit[0] from 0 to 1 and back to 0.

Note: The design must be reset whenever you begin a new test. The RESET_N pin of the Marvell PHY needs to be kept low for 10 ms because the minimum reset requirement of the Marvell PHY is 10 ms. - Open the config.tcl script using text editor, which is located in the <project_directory>/sc_tcl directory. Ensure that you set the following parameters accordingly to achieve intended operating speed rate and mode. For more information, refer to Configuration Script.

- Ensure that you set ETH_SPEED to 0 and to ENA_10 to 0 so that the MAC is not forced to operate at 1000 Mbps only. This allows the MAC to follow the speed rate of the PHY set in step 9.c.

- If you want to operate the MAC in 1000 Mbps only, set ETH_SPEED to 1. However, Intel does not recommend this setting because it causes link failure if the PHY is running at 10/100 Mbps only.

- Selection of speed rate:

- For 10 Mbps only, set PHY_ETH_SPEED to 10.

- For 10/100 Mbps only, set PHY_ETH_SPEED to 100.

- For 10/100/1000 Mbps, set PHY_ETH_SPEED to 1000.

- Ensure that you set the LOOP_ENA and PHY_LOOPBACK parameters to 0 so that the MAC/PHY loopback mode or PHY loopback mode is disabled.

- In the Intel® Quartus® Prime software, select to launch the System Console.

- In the System Console command shell, change the directory to <project_directory>/sc_tcl.

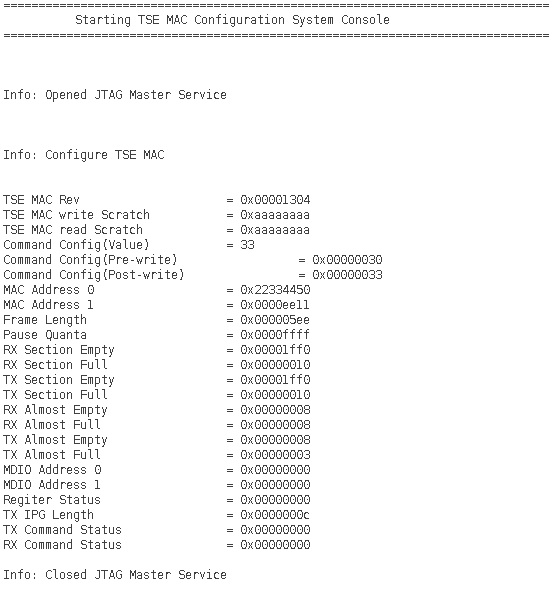

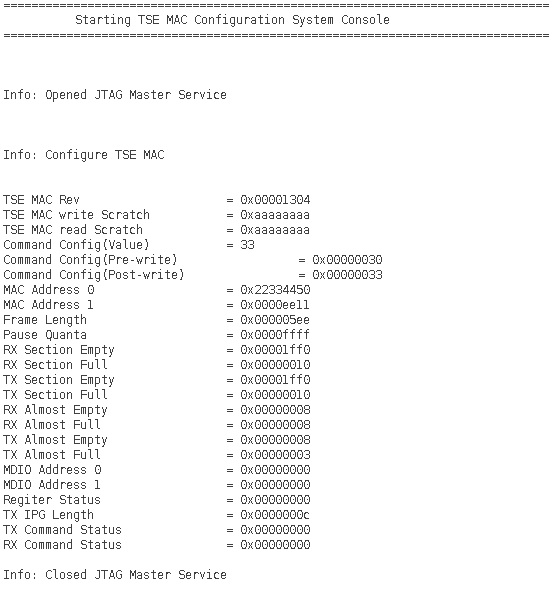

- Run the following command in the System Console command shell to start TSE MAC, TSE PCS, and on-board PHY chip configurations:

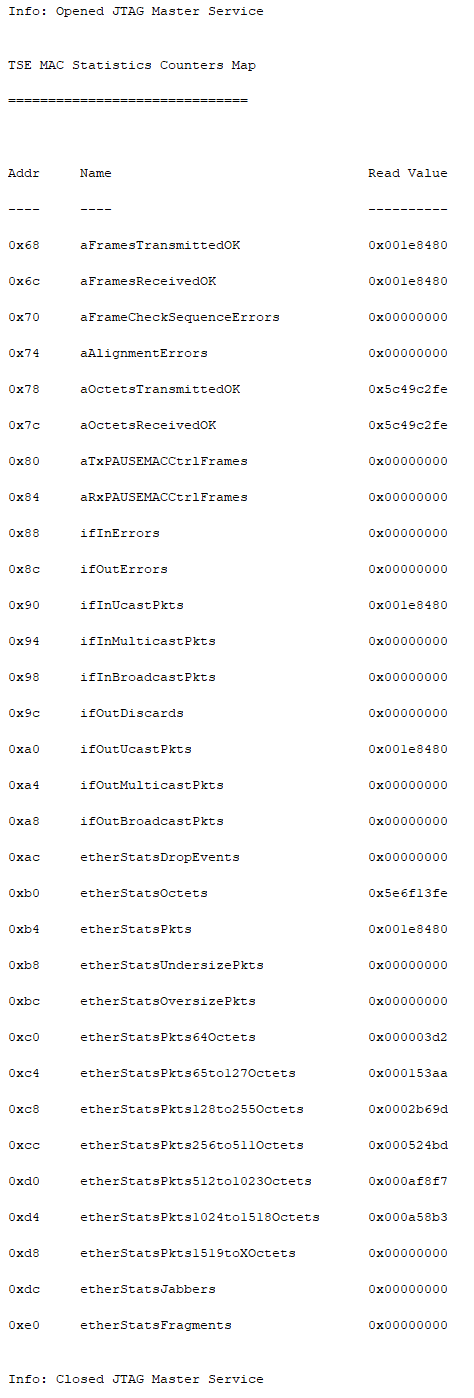

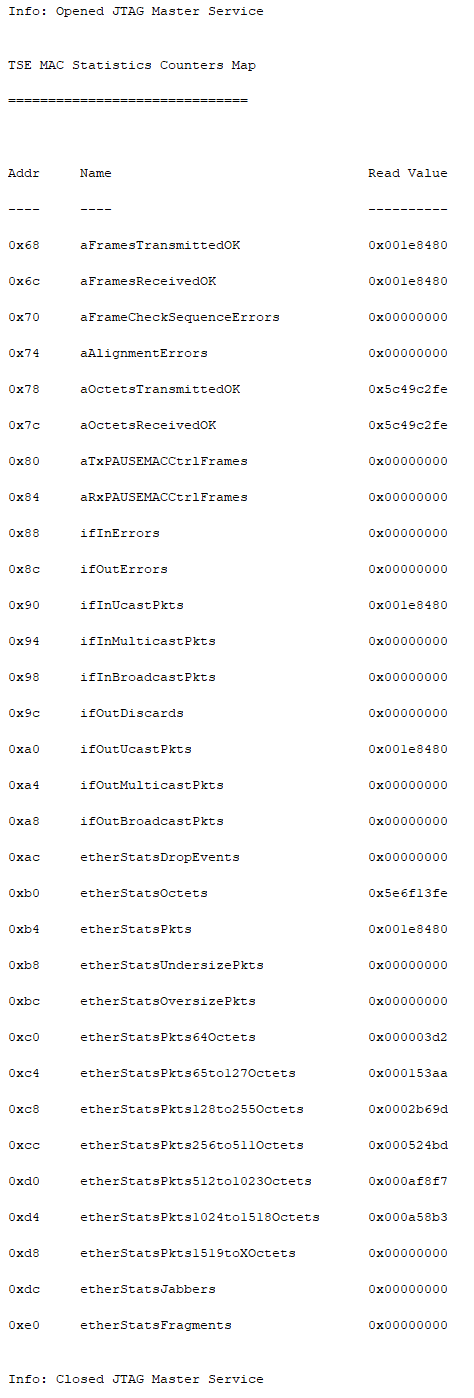

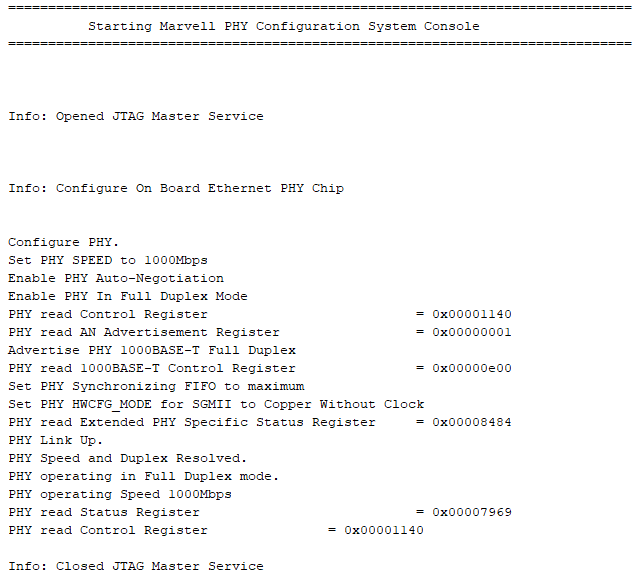

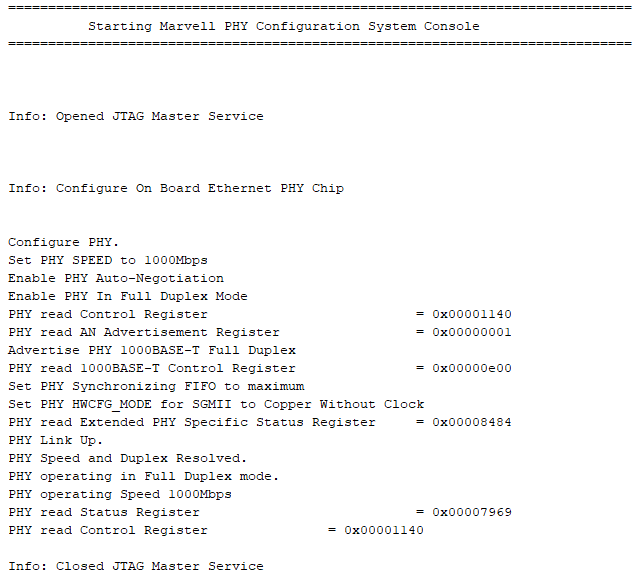

source config.tclThe System Console displays the copper link connection status and the resolved operating speed and duplex mode of on-board PHY Chip (refer to Figure 12).

- Start to transmit the Ethernet packets from the external packet generator to the development board. Verify the number of packets that successfully loop back to the external packet generator.

- Run the following command to view the TSE MAC statistic counters:

source tse_stat_read.tcl

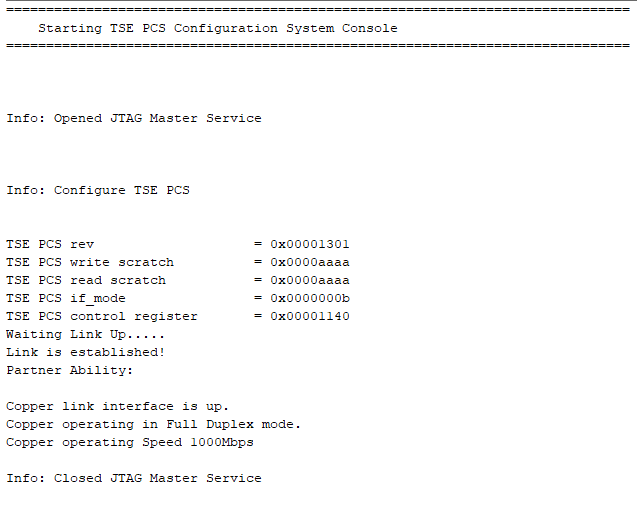

Figure 10. Sample Output—MAC Configuration Summary

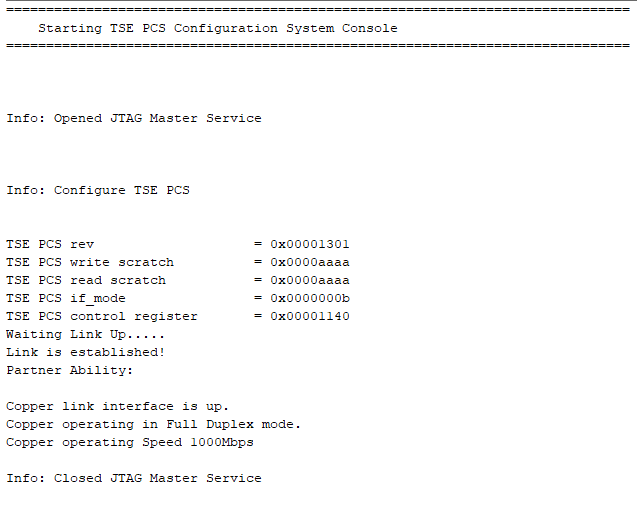

Figure 11. Sample Output—PCS Configuration Summary

Figure 12. Sample Output—On-Board PHY Chip Configurations

Figure 13. Sample Output—TX and RX MAC Statistic Counters