According to the pin placement requirements in Intel Agilex® 7 FPGA General-Purpose I/O and LVDS SERDES User Guide, each x4 DQ group shares the same OE, reset, and clock enable signals, therefore you cannot split the OE, Reset or clock enable signals within an x4 DQ group. Given the constraint, here are some considerations when placing I2C pins.

1. FPGA is used as an I2C master, requiring multi-master mode:

(i) A typical implementation of I2C is using OE on both SCL and SDA, as shown below. Thus, you cannot place SCL and SDA in the same x4 DQ group.

assign i2c_serial_scl_in = arduino_adc_scl;

assign arduino_adc_scl = i2c_serial_scl_oe ? 1'b0 : 1'bz;

assign i2c_serial_sda_in = arduino_adc_sda;

assign arduino_adc_sda = i2c_serial_sda_oe ? 1'b0 : 1'bz;

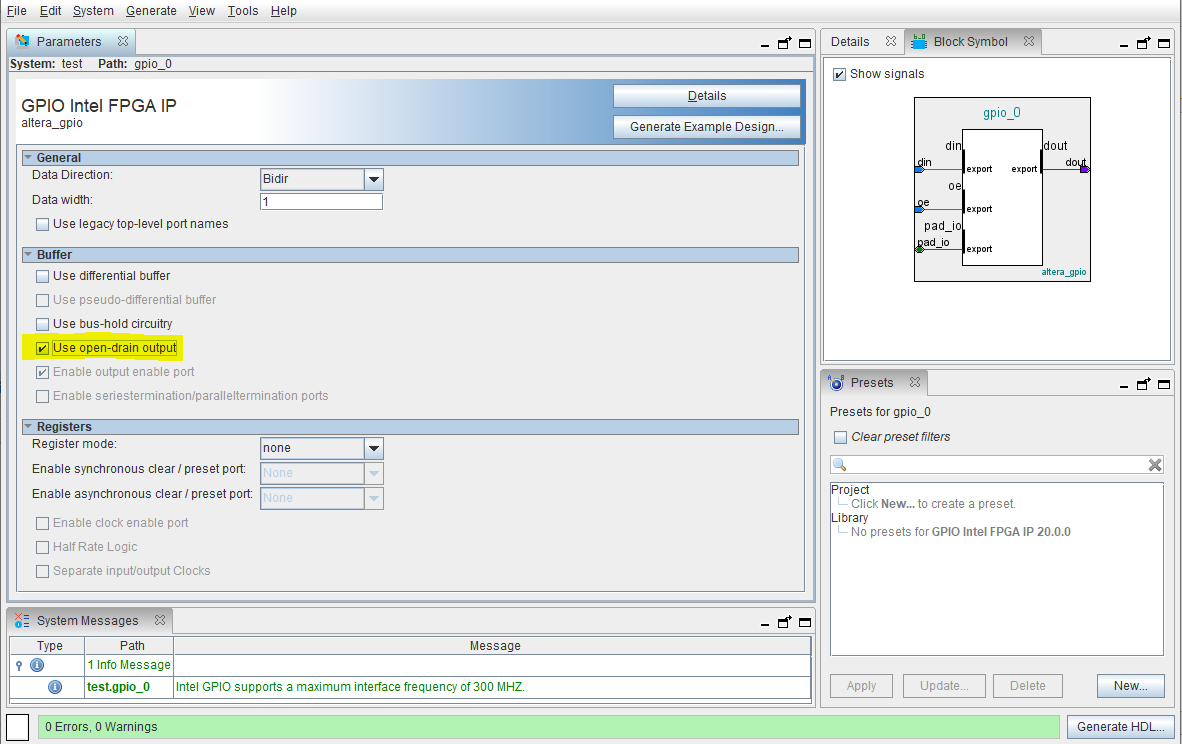

(ii) Another way is to use GPIO Intel FPGA IP. You can enable open-drain for SCL and SDA, connect both OE ports for SCL and SDA to 1 (high), and connect the inverted signals of the original OE control signals. In this way, you can work around the constraint. Following is an example:

gpioip gpioip_scl (

.dout (i2c_serial_scl_in),

.din (~i2c_serial_scl_oe),

.oe (1'b1),

.pad_io (arduino_adc_scl)

);

gpioip gpioip_sda (

.dout (i2c_serial_sda_in),

.din (~i2c_serial_sda_oe),

.oe (1'b1),

.pad_io (arduino_adc_sda)

);

2. FPGA is used as I2C master single mode:

SCL is an output pin without OE. SDA is a bidirectional pin with OE.

3. FPGA is used as I2C slave:

SCL is an input pin without OE. SDA is a bidirectional pin with OE.

In 2 and 3 above, because SCL doesn’t have OE,

- A SCL and a SDA can be assigned in the same x4 DQ group

- Multiple SCL and a SDA can be assigned in the same x4 DQ group

- Multiple SDA can’t be assigned in the same x4 DQ group

- When multiple SDA are assigned in the same x4 DQ group, using GPIO Intel FPGA IP as mentioned above is also a workaround.